Description

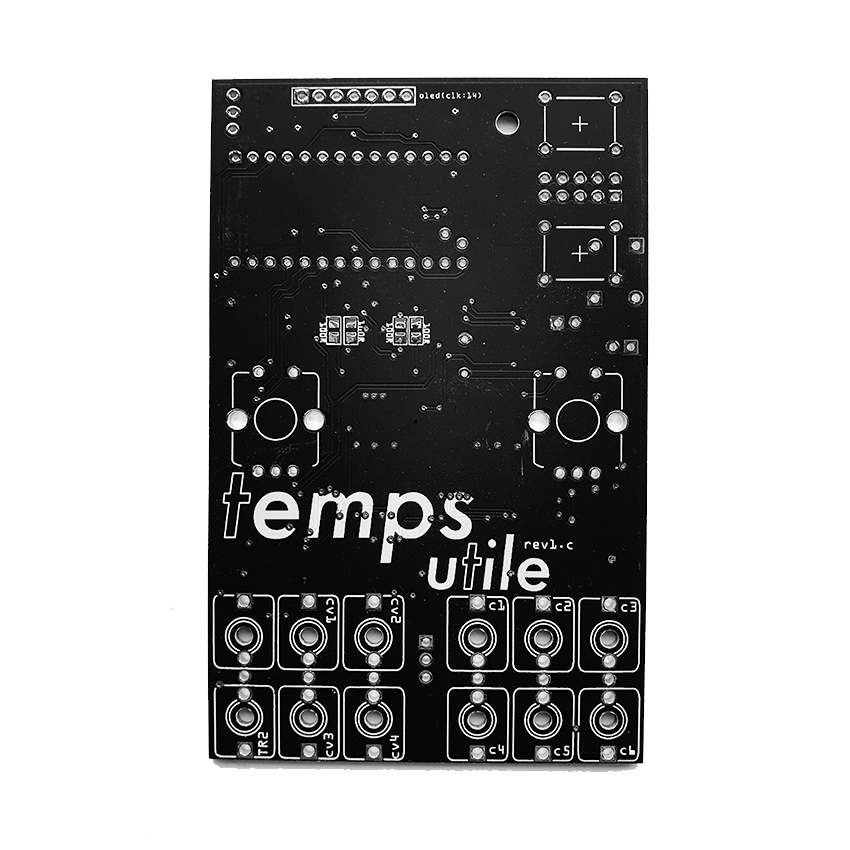

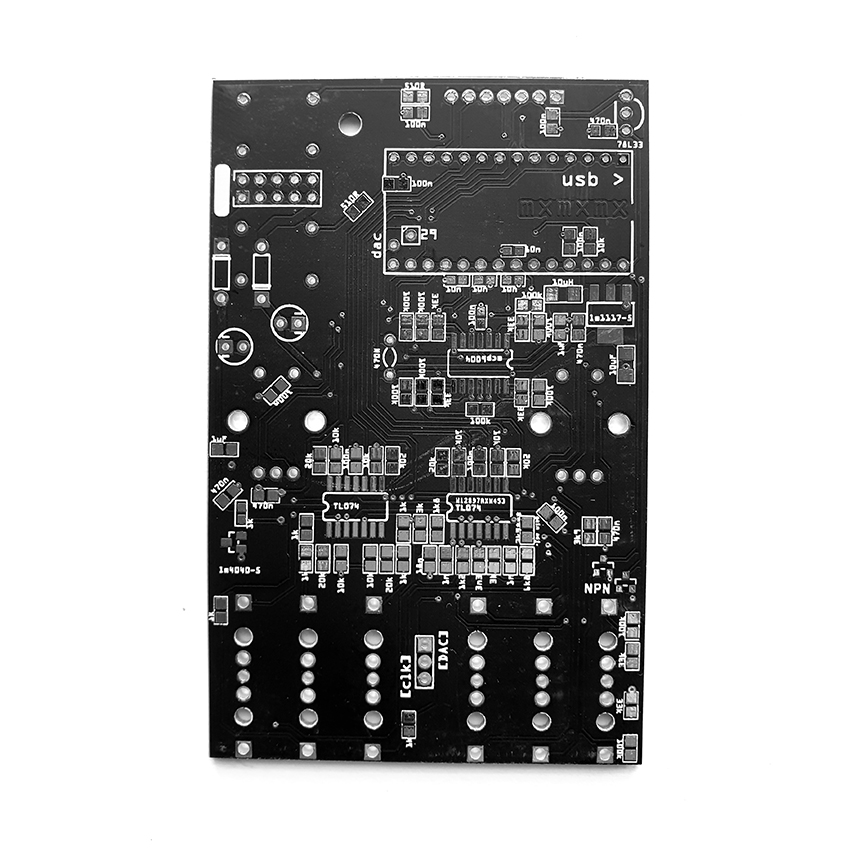

hardware basics, in brief:

- teensy 3.1/3.2 @ 120MHz, w/ 128×64 OLED

- trigger-to-output latency < 100us.

- 2 clock inputs (> 100k input impedance; threshold ~ 2.5V)

- 4 CV inputs (100k input impedance, -/+ 5V, assignable to (almost) any parameter)

- 6 clock outputs (5 digital, 1 DAC (12 bit): 10V (GPIO), -/+ 5V (DAC))

- two encoders w/ switches; 2 tactile buttons.

- 14HP, ~ 25 mm Depth

firmware:

-

7 modes, selectable per channel:

- trigger sequencer/sequence editor

- clock division/multiplication

- LFSR

- random w/ threshold

- euclidian

- logic (AND, OR, XOR, NAND, NOR, XNOR)

- burst

- DAC (channel #4 only): random, binary, lfsr (“Turing”), logistic, sequencer/arpeggiator